题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

若4位二进制加法计数器正常工作时,由0000状态开始计数,则经过43个输入计数脉冲后,计数器的状态应该是()。

A.0011

B.1011

C.1101

D.1110

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码进入小程序

拍照、语音搜题,请扫码进入小程序

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.0011

B.1011

C.1101

D.1110

答案

答案

更多“若4位二进制加法计数器正常工作时,由0000状态开始计数,则经过43个输入计数脉冲后,计数器的状态应该是()。”相关的问题

更多“若4位二进制加法计数器正常工作时,由0000状态开始计数,则经过43个输入计数脉冲后,计数器的状态应该是()。”相关的问题

第1题

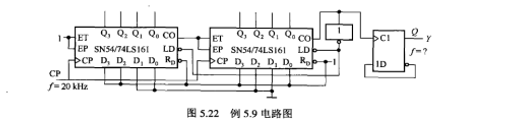

由两片SN54/74LS161(同步4位二进制计数器)组成的同步计数器如图5.22所示.

1)试分析其分频比(即Y与CP之频比),当CP的频率为20kHz时,Y的频率为多少?

2)试用2片SN54/74LS161组成模为91的计数器,要求两片间用级联法,并工作可靠.

第2题

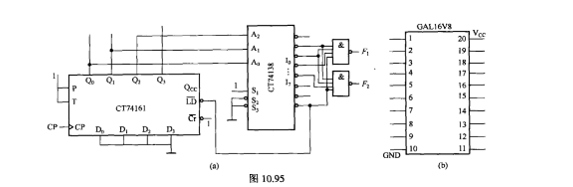

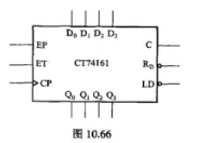

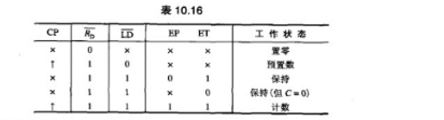

转换图.假设Q3Q2Q1Q0的初始状态均为0,说明CT74161构成几进制计数器.

(2)说明C174138电路实现的功能.

(3)写出图10.95(a)完成的电路功能符合ABEL语言(GAL16V8如图10.95(b)所示)或VHDL语言的用户原文件(可省略测试向量段).

第3题

第4题

第5题

A.同步4位二进制计数器,具有同步清零功能

B.同步4位二进制计数器,具有异步清零功能

C.同步8421BCD十进制计数器,具有异步清零功能

第6题

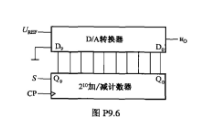

试用 Verilog语言描述一个4位二进制可逆计数器的行为。要求如下:

(1)电路具有5种功能,即异步清零、同步置数、递增计数、递减计数和保持原有状态不变。且要求计数器能输出进位信号和借位信号,即当计数器递增计数到最大值时,产生一个高平有效的进位信号C0;当计数器递减计数到最小值0时,产生一个高电平有效的借位信号B0。

(2)用QuartusI软件进行逻辑功能仿真,并给出仿真波形。

第10题

第11题