题目内容

(请给出正确答案)

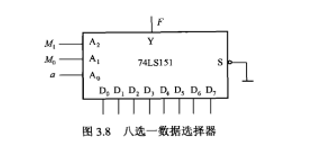

题目内容

(请给出正确答案)

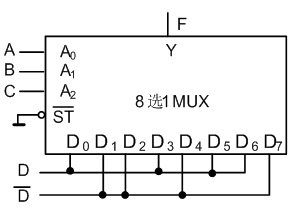

下图所示为双4选1数据选择器构成的组合逻辑电路,输入变量为A、B、C,输出F1、F2的逻辑函数分别为 、 ,其功能为 。

A.输出F1、F2的逻辑函数分别为 、 ,其功能为 。 #图片0$#

B.#图片1$#,#图片2$#,全加器

C.#图片3$#,#图片4$#,全减器

D.#图片1$#,#图片6$#,全加器

E.#图片7$#,#图片2$#,全减器

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码进入小程序

拍照、语音搜题,请扫码进入小程序

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.输出F1、F2的逻辑函数分别为 、 ,其功能为 。 #图片0$#

B.#图片1$#,#图片2$#,全加器

C.#图片3$#,#图片4$#,全减器

D.#图片1$#,#图片6$#,全加器

E.#图片7$#,#图片2$#,全减器

答案

答案

更多“下图所示为双4选1数据选择器构成的组合逻辑电路,输入变量为A、B、C,输出F1、F2的逻辑函数分别为 、 ,其功能为 。”相关的问题

更多“下图所示为双4选1数据选择器构成的组合逻辑电路,输入变量为A、B、C,输出F1、F2的逻辑函数分别为 、 ,其功能为 。”相关的问题

第1题

第3题

A、一个“检1”电路,即输入(DCBA)中包含奇数个‘1’时,输出为‘1’

B、一个“检1”电路,即输入(DCBA)中包含偶数个‘1’时,输出为‘1’

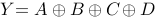

C、一个四变量异或电路,即

D、一个四变量同或电路,Y=A⊙B⊙C⊙D

第5题

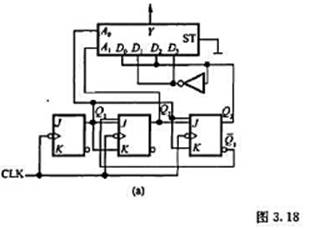

图3.18(a)是一种序列信号发生器电路,它由一个计数器和一个四选一数据选择器构成.分析计数器的工作原理,确定其模值和状态转换关系,确定在计数器输出控制下,数据选择器的输出序列.

第6题

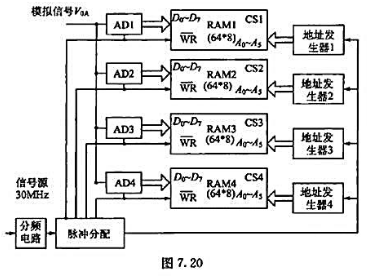

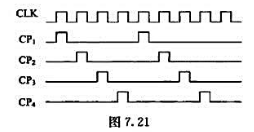

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第10题

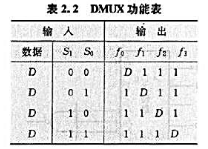

1:4线数据分配器(DMUX)的逻辑功能表见表2.2所示.请设计DMUX的内部逻辑电路图.

第11题

一、设有一学生-课程数据库,其中关系表如下所示: 学生关系表:Student(Sno,Sname,Ssex,Sage,Sdept) 课程表关系:Course(Cno,Cname,Cpno,Ccredit) 学生选课表:SC(Sno,Cno,Grade) 请用SQL语句实现下列各题: (1)建立一个“学生”表SC。 (2)为学生-课程数据库中的SC建立索引,SC表按学号升序和课程号降序建索引。 (3)查询全体学生的详细记录。 (4)查询年龄在20~23岁(包括20岁和23岁)之间的学生的姓名、系别和年龄。 (5)查询名字中第2个字为"明"字的学生的姓名和学号。 (6)查询学生总人数。 (7)查询选修了课程M01或者选修了课程M02的学生。 (8)将学生08001的年龄改为23岁。