题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

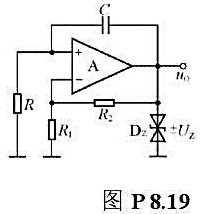

图P8.19所示电路为某同学所接的方波发生电路,试找出图中的三个错误,并改正.

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码进入小程序

拍照、语音搜题,请扫码进入小程序

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“图P8.19所示电路为某同学所接的方波发生电路,试找出图中的三个错误,并改正.”相关的问题

更多“图P8.19所示电路为某同学所接的方波发生电路,试找出图中的三个错误,并改正.”相关的问题

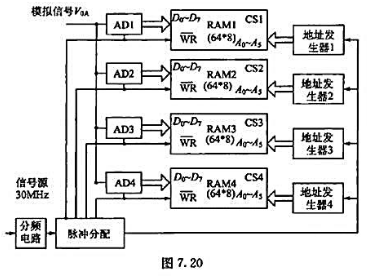

第1题

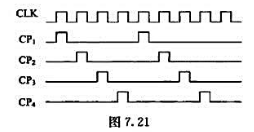

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

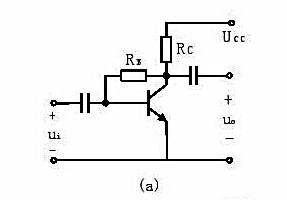

第4题

题7.4图(a)所示电路为集电极——基极偏置放大电路,设三极管的β值为50,VCC=20V,RC=10kΩ,RB=330kΩ。

(1)估算电路的静态工作点;

(1)估算电路的静态工作点;

(2)若接上2kΩ的负载电阻,计算电压放大倍数和输入电阻。

第5题

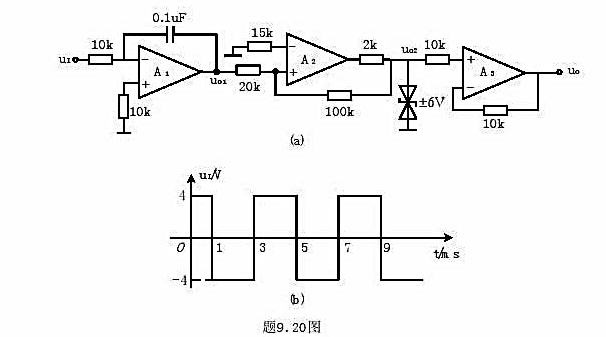

题9.20图(a)所示电路中,输入电压ur的波形如图(b)所示,已知电容的初始电压为零。(1)指出A1、A2、A3各组成何种电路;(2)画出各输出电压u01、u02和u0的波形,标出有关电压值。

第7题

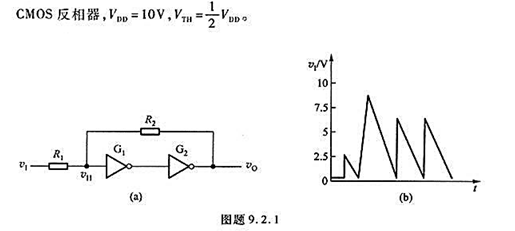

在图题9.2.1所示的施密特触发器电路中,已知R1=10kΩ,R2=20kΩ。G1、G2为

(1)试计算电路的正向阈值电压VT+、负向阈值电压VT-和回差电压ΔVT。

(2)若电路的输入信号v1波形如图题9.2.1(b)所示,试画出相应的输出电压v0的波形。

第9题

图4.15(a)所示为存储器的地址空间分布图,其中已配备了ROM1、ROM2、RAM1、RAM2,请设计对应地址空间的地址译码电路.

第10题

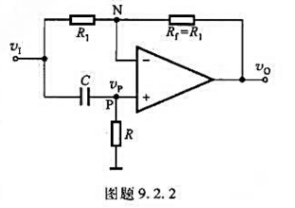

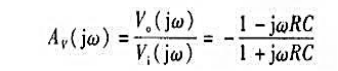

图题9.2.2所示是一阶全通滤波电路的一种形式。(1)试证明电路的电压增益表达式为 (2)试求它的幅频响应和相频响应,说明当w由0→∞时,相角ϕ的变化范围。

(2)试求它的幅频响应和相频响应,说明当w由0→∞时,相角ϕ的变化范围。